Important considerations in Digital IC Design

As we all know, the recent topic of chip design and manufacturing still occupies people's time before and after tea. The encirclement and interception of the enemy makes us abandon our illusions and rise up to fight. In our work or life, no matter in the upstream or downstream of the semiconductor industry, we can't avoid the chip. Without it, we can't do anything.

When you turn on the air conditioner at home, take out a bottle of ice coke from the refrigerator, and ge you lies down with his mobile phone to brush the video, you want the video to be smooth and free of jamming. Behind this, there are groups of chip design engineers, mobile communication engineers, network engineers, image processing engineers, chip development / verification engineers, chip manufacturing engineers, chip packaging and testing engineers... Working day and night.

The design of any chip requires the close cooperation of a huge design and verification team. In chip design, we need to consider many factors. So, what are we thinking in our minds?

The triple realm of chip logic development engineer: circuit in mind, sequence in brain and code in hand.

If we use synchronous design or any IP in the design, or finalize the architecture and microarchitecture, we need to develop various strategies. Some of them are listed below:

Design functionality and compatibility

Parallelism, concurrency and pipeline strategy

External IO and high speed interface

Design area and initial gate number estimation

Speed and maximum frequency requirements

Power requirements and low power design

Clock network and delay

Interface and IO latency and modeling strategy

After the above considerations, a team composed of experienced technicians finally determines the architecture and microarchitecture of ASIC / SOC design.

In order to understand the architecture and project R & D, we need to consider some design factors, mainly in the following aspects.

01

timing parameters

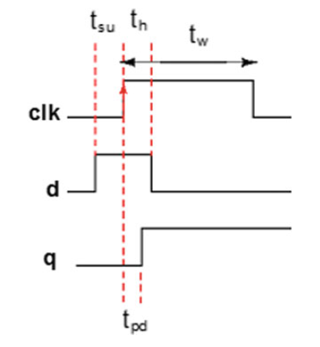

The important timing parameters of the rising edge sensitive trigger are shown in Figure 1. They are:

Establishment time (TSU)

Holding time (th)

Trigger propagation delay (TPD)

Fig. 1 timing parameters of D trigger

Establishment time (TSU): the minimum time that the data input of the trigger should maintain a stable value before the effective edge of the clock arrives is called the establishment time.

The effective edge indicates the jump of the D trigger sensitive to the rising edge (positive edge) from low level to high level, and the D trigger sensitive to the falling edge (negative edge) from high level to low level.

During the establishment time window, if the data input is from 1 to 0 or vice versa, the trigger output will be metastable, indicating an establishment violation.

Hold time (th): the minimum time that the data input of the trigger remains stable after the effective edge of the clock arrives, which is called hold time.

The effective edge represents the jump from low to high of the D trigger sensitive to the rising edge (positive edge) and from high to low of the D trigger sensitive to the falling edge (negative edge).

During the hold time window, if the data input is from 1 to 0 or vice versa, the trigger output will be metastable, indicating a hold violation.

Propagation delay of trigger (TPD = TCQ): the time required for the trigger to produce effective output after reaching the effective edge of the clock, which is called the propagation delay of the trigger.

The propagation delay is also known as the delay from the clock to the Q end, also known as TCQ.

02

Metastable state

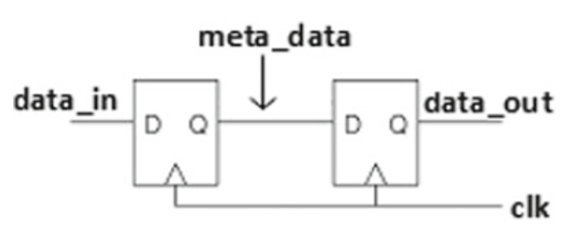

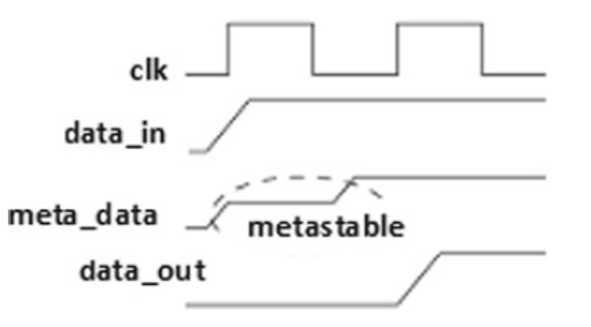

If the data input of the design shown in Fig. 2 is connected to another module whose clock is generated by different clock sources, the first trigger output will be in metastable state.

Meta data indicates that the trigger data is metastable, so the first trigger has a timing violation. Metastable state indicates that the data output is invalid. In order to obtain effective data output, the design needs to use multi-level synchronizer.

The timing of the data sampled by the first trigger and the output of the second trigger is shown in Fig. 3. As shown in the figure, the output of the first trigger is in metastable state, and the data out output of the output trigger is in legal and valid state.

Figure 2 level synchronization

Fig. 3 metastable level synchronization timing

03

Clock Skew

If there are multiple clocks in ASIC design, clock distribution and clock tree synthesis will play a very important role in balancing the clock skew between different clock inputs of each block.

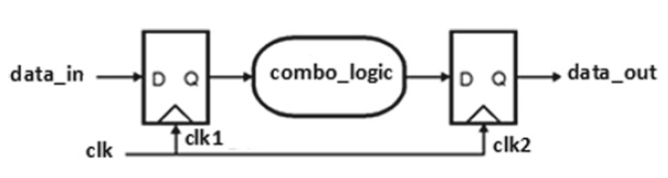

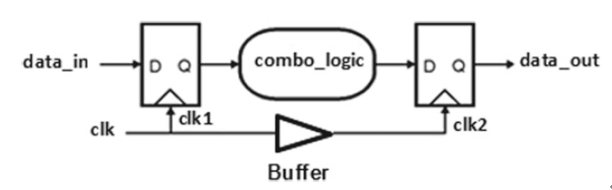

If two different clocks in the design arrive at different time instances, the design has clock skew. The reason for the clock offset is the routing delay, that is, the line delay designed in the single clock domain. Considering the diagram shown, let's consider that the CLK edge of the transmitting trigger arrives at time instance t0 and the trigger is captured at time instance T2. Because the clock arrival time of this synchronous design is different, there is a phase shift between CLK1 and CLK2, which can be considered as clock offset. Another reason is the aging of the oscillator; Then, the clock cycle frequency generated by the oscillator changes, so the difference in arrival time can be called jitter.

Figure 4 synchronous design

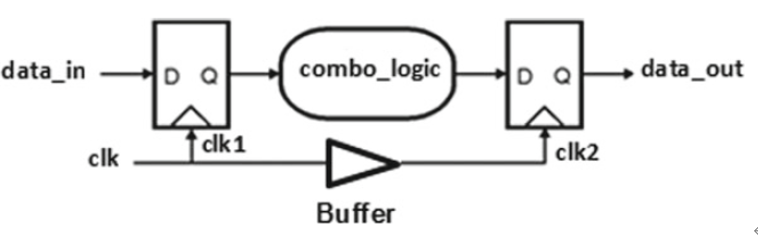

In Fig. 4, the clock skew is caused by the interconnection delay between CLK1 pin and CLK2 pin.

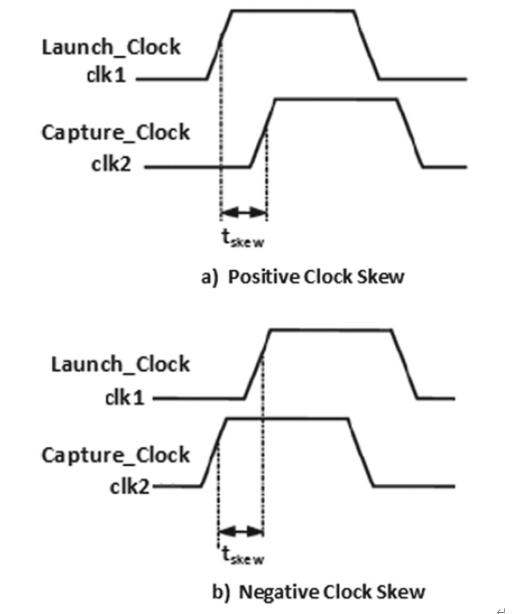

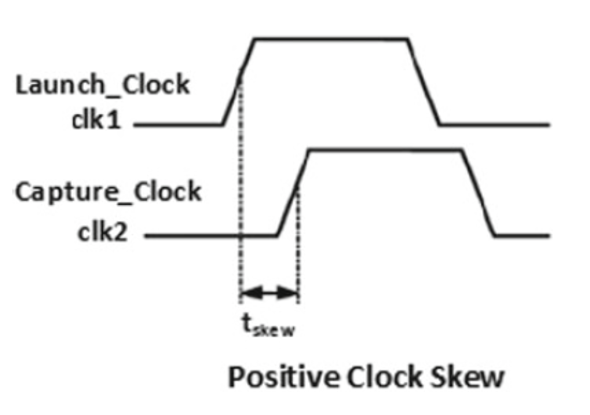

In the actual ASIC design, we experienced two different types of bias, as shown in Figure 5.

Positive clock offset: indicates that the transmit clock CLK1 is triggered first and then the capture clock CLK2 is reached. As shown in tskew, it is the difference between the arrival times of CLK1 and CLK2. In other words, we can imagine that the positive clock skew is that the data and clock run in the same direction. The positive clock skew is conducive to the establishment of time, but it is not good for the holding time, because there is a positive margin to manage.

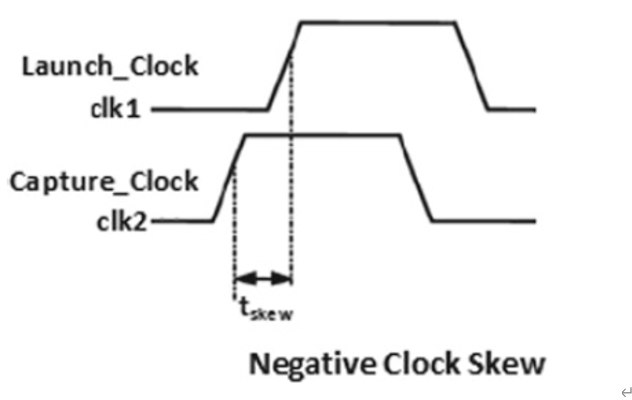

Negative clock offset: the last trigger is the transmit clock CLK1, and the first trigger is the capture clock CLK2. As shown in tskew, it is the difference between the arrival times of CLK1 and CLK2. In other words, we can imagine that the negative clock offset is that the data and clock run in the opposite direction. The negative clock offset is better for the holding time, but not for the establishment time.

Figure 5 offset in design

In ASIC design, we always encounter clock skew caused by jitter or interconnection (i.e. line delay). Here are the key points we should know.

Positive clock skew is conducive to establishing time, but not conducive to maintaining time.

Negative clock skew is conducive to maintaining time, but not conducive to establishing time.

Positive clock skew

As discussed earlier, the positive clock skew transmit flip-flop is triggered first and then captured at the capture flip-flop. There is a buffer delay margin between the transmit clock and the capture clock, which can be used to improve the frequency required by the design.

Figure 6 shows the synchronous design of clock forward skew. The skew between CLK1 and CLK2 is tbuffer.

Figure 6 positive clock skew

Let's find out the required data time and data arrival time.

Data Arrival Time(AT)=tpff1+tcombo

Dara Required Time(RT)=Tclk+tbuffer-tsu

Where TCLK is the clock cycle or the delay from the clock to the Q terminal. Tbuffer is the buffer delay, TSU is the trigger setup time, tpff1 is the trigger propagation delay, and tcombo is the combinational logic delay.

Setup slack is the difference between the time required for data and the arrival time of data, which should be positive. A positive build time margin indicates that there are no build violations in the design. In order to avoid the establishment violation in the design, the design should have fast data, fast start clock (CLK1) and slow capture clock (CLK2). In other words, the actual arrival of data should be faster than the required data time. (as shown in Figure 7)

Fig. 7 the relationship between trigger and capture clock is positive clock skew

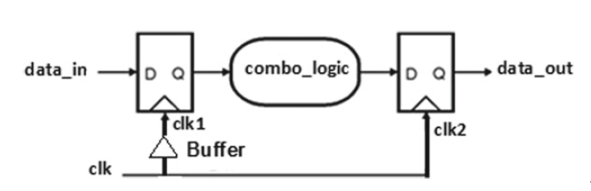

Negative clock skew

As discussed earlier, the negative clock skew is triggered at the end of the transmit trigger and the capture trigger is triggered first. Due to the margin of buffer delay between trigger clock and capture clock, this reduces the maximum frequency of the design.

Figure 8 shows the synchronization design of negative clock offset. The offset between CLK1 and CLK2 is tbuffer.

Let's find out the required data time and data arrival time.

Data Arrival Time(AT)=tbuffer+tpff1+tcombo

Dara Required Time(RT)=Tclk-tsu

Figure 8 negative clock skew

Fig. 9 the relationship between trigger and capture clock is negative clock skew

04

Allowance (slack)

In ASIC design, there are two terms used to describe margin, namely, setup slack and hold slack.

Figure 10 register to register path in synchronous design

Setup slack

The establishment margin is the difference between the data required time and the data arrival time, which should be positive. A positive build margin indicates that there are no build violations in the design.

Data Arrival Time(AT)=tbuffer+tpff1+tcombo

Dara Required Time(RT)=Tclk-tsu

Setup Slack=RT-AT

Hold slack

The retention margin is the difference between the data arrival time and the data demand time, which should be positive. Positive retention margin indicates that there are no retention violations in the design.

05 clock delay

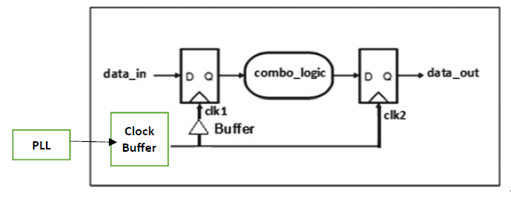

The clock is generated by the phase-locked loop and used for the design of single clock domain. For multiple clock domains, we may need multiple phase-locked loops.

The clock network introduces delay, which is actually the time required for the clock to reach the chip. The clock delay is caused by the clock network delay in the process of clock distribution.

Figure 11 clock network delay

06

Designed area

The total area of ASIC is composed of standard unit, macro and IP core. In the design of one million or one hundred million gates of integrated circuits, area constraints and better layout planning play an important role in obtaining the expected performance. We can consider area optimization at different design stages, such as:

In the process of architecture design, better strategies are obtained through the interactive description of different function blocks.

In the process of RTL design, tool based instructions and commands are used, and resource sharing technology is used.

In the physical design of layout stage, function blocks are placed through strategies to minimize the area consumption caused by wiring delay and the use of wiring resources.

07

Speed requirements

Speed is another important consideration in ASIC design. Using different speed improvement techniques can improve the performance of ASIC. For example, considering that the processor is designed to work at 500MHz, we are faced with the challenge of improving the design frequency. In this case, various strategies can be used in the ASIC design cycle, but they may be rarely used:

It has good sequence boundary division in the design of architecture and microarchitecture.

In the initial layout, interdependent blocks can be placed close to each other to minimize the area, so as to reduce the wiring delay and improve the speed.

In the RTL design stage, the balance register and register copy and optimization commands are used to improve the design performance. But they may affect the logical area.

In the process of RTL design, the input and output of registers are used to make the design have better performance.

Use the concept and architecture of pipelining whenever possible.

If you need to use FSM design and controller in the design, try to work on control and data path synthesis to obtain clean timing and better performance.

Try to use synchronous designs because they are faster than asynchronous designs.

Try to avoid internal clock generator; Instead, consider the clock tree and optimize the clock tree during CTS.

In the cabling phase, try to use improved tool based technology, because enabling tool instructions can play a particularly important role in balancing clock skew.

08

Power consumption requirements

For any type of ASIC or SoC design, the important consideration is power, and the goal of the design team is to reduce leakage and dynamic power consumption. In the process of physical design, power constraints are considered for power planning. In different stages of ASIC design process, power optimization technology should be adopted.

ASIC architecture with low power consumption awareness.

Use UPF at different design levels.

During RTL, in order to minimize dynamic power, a dedicated clock gating unit is used.

Power can also be optimized in the RTL phase by avoiding unnecessary data value allocation and switching.

In the process of physical design, there is better power planning and power sequencing for multiple power domains.

There is a good power-off strategy in the physical design process.

09

Design constraints

Design constraints are basically design rule constraints and optimization constraints. We can consider these constraints as module level constraints, top-level constraints and chip level constraints.

Design rule constraints (DRC): we can regard these constraints as the rules of chip manufacturers and should meet them. During the physical design process, we will check whether all DRC rules of the chip manufacturer are met. Layout is clean indicates that there is no DRC violation. These constraints are mainly:

Transition

Fanout

Capacitance

Optimization constraints: these constraints are used during the design and optimization phases. These are the main constraints

Area

Speed

Power

Mainly using Synopsys DC, we will take advantage of area and speed constraints and try to optimize the design in each optimization stage.

Physical design tools, such as Synopsys IC compiler, use the constraints of area, speed and power to meet the final constraints and realize clean chip layout.